I’m a passionate Physical Design Engineer with hands-on experience in executing complex ASIC design flows from RTL to GDSII across advanced technology nodes including 5nm, 14nm, and 28nm. I specialize in Place and Route (PnR), Static Timing Analysis (STA), and power-aware design, with a strong focus on optimizing Power, Performance, and Area (PPA) under multi-corner multi-mode (MCMM) scenarios. With a proven track record working on AI accelerators and data center processors, I’ve contributed to successful tape-outs by addressing IR-drop, crosstalk, and timing closure challenges using industry-standard EDA tools like Synopsys ICC2, Design Compiler, PrimeTime, StarRC, and Cadence Innovus. I also develop efficient automation scripts in TCL to streamline physical design and STA workflows, ensuring rapid design convergence and sign-off accuracy.

Standard Cell-Based ASIC Design for 8-bit Accumulator

Implemented Verilog code and Testbench for the 8-bit Accumulator, then synthesized the RTL codes. Executed Logical Synthesis process using DC tool, and recorded area, power, and timing reports. Performed PnR using Encounter. After PnR buffers are added and then performed Post PnR and recorded optimized area, power, and timing results, and performed Formal verification. Collected GDSII file and plotted the final Layout. .

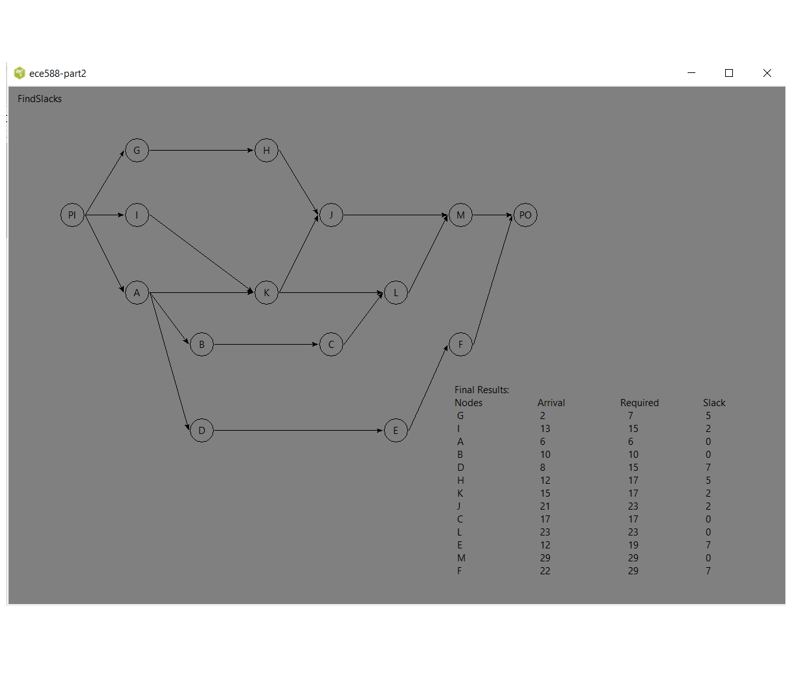

CAD Tool Design for Static Timing Analysis by using Tcl/Tk and C

Designed C code to calculate the required time, arrival time, and slack time from the given input matrix file and save the output file separately. Designed a Static Timing Analysis CAD tool GUI using TCL/Tk, which can take inputs from the user and optimize the given input matrix using implemented C code and display the output results on the GUI interface. .

Hierarchical Schematic and Layout Design of 4-bit Carry Look-ahead Adder

Designed a 4-bit CLA adder schematic, Symbol, Testing Circuit, and Layout using Virtuoso. Performed LVS, DRC, and PEX using MG Calibre. Then Formal verification is performed using Formality. Measured Power, Delay, and temperature using HSPICE. .